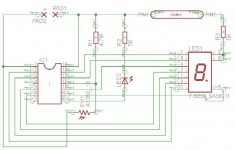

Das ist mir schon klar - hätte ich vielleicht hinschreiben sollen - und trifft auch das was schon zu den undefinierten Entladeströmen gesagt wurde.waste1 schrieb:Es ist normal, dass digitale Eingänge (CMOS) bei VCC/2 am Eingang einen erhöhten Querstrom zeigen. Da sind dann beide Eingangstransistoren teilweise leitend.

Auch das ist bekanntwaste1 schrieb:Das ist auch bei ganz normalen CMOS-Gattern der Fall. Deshalb soll man auch offene (floatende) Eingänge vermeiden.

Nur das ist eben nicht möglich, wenn man einen Pinchange-IRQ nutzen willwaste1 schrieb:Den digitalen Eingang kann man bei den AVRs abschalten. Wichtig beim normalen RL mit ADC!

Ich sage doch gar nicht, dass ich die Messungen anzweifle, ich bin halt nur leicht skeptisch, wie groß der Einfluss des zusätzlichen Stroms über den Spannungsteiler ist.

Viele Grüße,

Thomas(_st)